光刻技術是推動集成電路芯片制程工藝持續微縮的核心驅動力之一。近日,北京大學化學與分子工程學院彭海琳教授團隊及合作者通過冷凍電子斷層掃描(cryo-electron tomography,cryo-ET)技術,首次在原位狀態下解析了光刻膠分子在液相環境中的微觀三維結構、界面分布與纏結行為,指導開發出可顯著減少光刻缺陷的產業化方案。相關論文近日刊發于《自然-通訊》。

“顯影”是光刻的核心步驟之一,通過顯影液溶解光刻膠的曝光區域,將電路圖案精確轉移到硅片上。光刻膠如同刻畫電路的顏料,它在顯影液中的運動,直接決定電路畫得準不準、好不好,進而影響芯片良率。長期以來,光刻膠在顯影液中的微觀行為是“黑匣子”,工業界的工藝優化只能靠反復試錯,這成為制約7納米及以下先進制程良率提升的關鍵瓶頸之一。

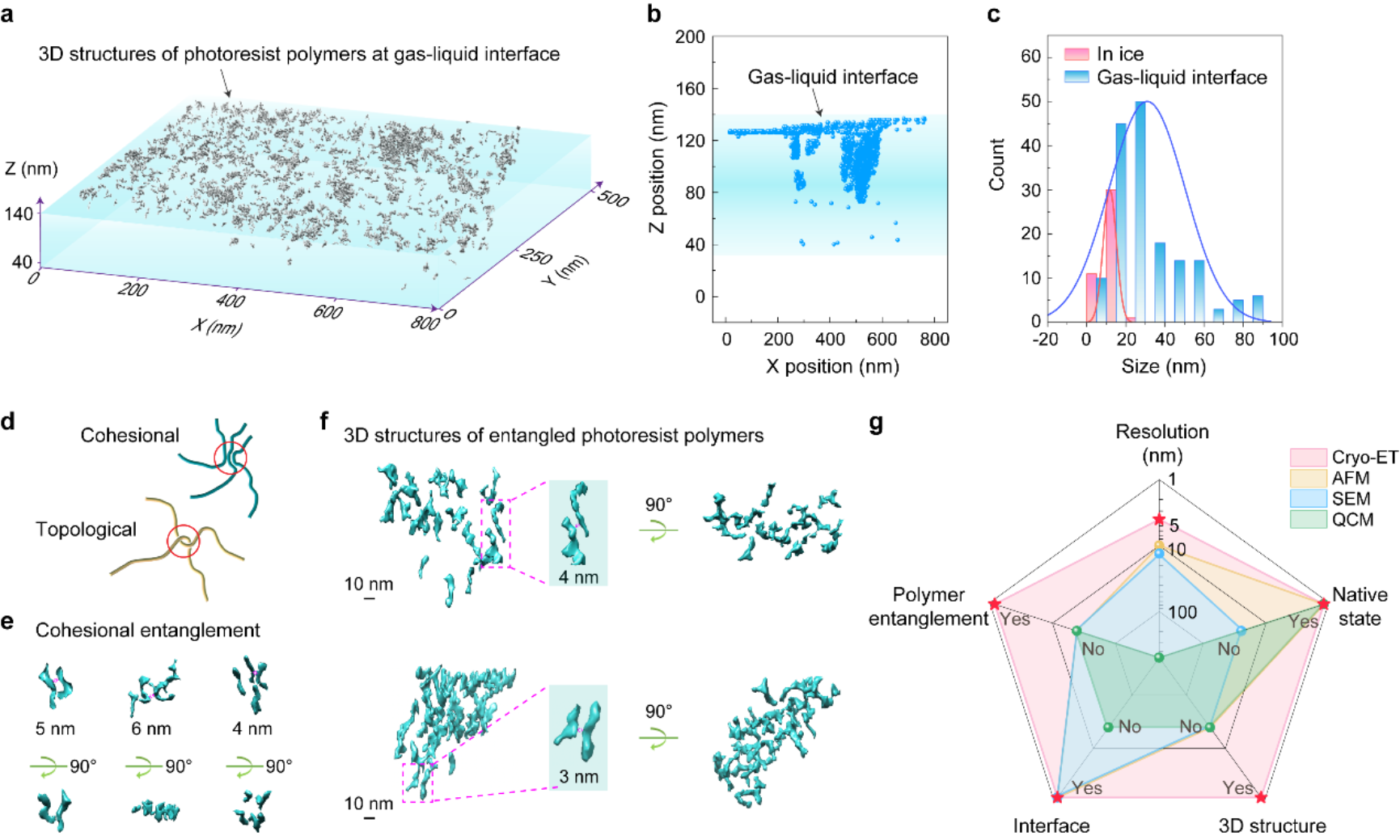

為破解難題,研究團隊首次將冷凍電子斷層掃描技術引入半導體領域。他們在晶圓上進行標準的光刻曝光后,將含有光刻膠聚合物的顯影液快速吸取到電鏡載網上,并在毫秒內將其急速冷凍至玻璃態,“定格”光刻膠在溶液中的真實狀態。

隨后,研究人員在冷凍電鏡中傾斜該樣品,采集一系列傾斜角度下的二維投影圖像,再基于計算機三維重構算法,將這些二維圖像融合成一張高分辨率的三維視圖,分辨率優于5納米。這種方法一舉解決了傳統技術無法原位、三維、高分辨率觀測的三大痛點。

該技術帶來諸多新發現。論文通訊作者之一、北京大學化學與分子工程學院高毅勤教授介紹,以往業界認為溶解后的光刻膠聚合物主要分散在液體內部,然而三維圖像顯示它們大多吸附在氣液界面;團隊還首次直接觀察到光刻膠聚合物的“凝聚纏結”,其依靠較弱的力或者疏水相互作用結合;而且,吸附在氣液界面的聚合物更易發生纏結,形成平均尺寸約30納米的團聚顆粒,這些“團聚顆粒”正是潛在的缺陷根源,它們容易沉積到精密的電路圖案上,讓本該分開的電路連在一起。

團隊為控制纏結提出了兩項實用方案:適當提高曝光后烘烤溫度,抑制聚合物纏結,減少大團聚體生成;優化顯影工藝,讓晶圓表面始終有連續液膜,使其可以帶走聚合物,避免其沉積。兩種方案結合,12英寸晶圓表面的光刻膠殘留物引起的圖案缺陷被成功消除,缺陷數量降幅超過99%。

彭海琳表示,冷凍電子斷層掃描技術為在原子/分子尺度上解析各類液相界面反應提供了強大工具。深入掌握液體中聚合物的結構與微觀行為,可推動先進制程中光刻、蝕刻和濕法清洗等關鍵工藝的缺陷控制與良率提升。

友情鏈接: 政府 高新園區合作媒體

Copyright 1999-2025 中國高新網chinahightech.com All Rights Reserved.京ICP備14033264號-5

電信與信息服務業務經營許可證060344號主辦單位:《中國高新技術產業導報》社有限責任公司